Journal of Robotics, Networking and Artificial Life

Vol. 7(1); June (2020), pp. 7–11

DOI: https://doi.org/10.2991/jrnal.k.200512.002; ISSN 2405-9021; eISSN 2352-6386

https://www.atlantis-press.com/journals/jrnal

#### Research Article

# Research on a Bridgeless Interleaved PFC Boost Converter with Voltage Doubler Feature

Chih-Chiang Hua<sup>1</sup>, Ching-Chun Chuang<sup>1,\*</sup>, Hung-Chi Lee<sup>2</sup>, Chih-Wei Chuang<sup>1</sup>, Chuan-Ming Niu<sup>1</sup>

- Department of Electronical Engineering, National Yunlin University of Science and Technology, No. 123, University Rd., Section 3, Douliu, Yunlin 64002 Taiwan

- <sup>2</sup>Department of Electronics and Computer Engineering, National Taiwan University of Science and Technology, No. 43, Section 3, Keelung Rd., Taipei City 106, Taiwan

#### **ARTICLE INFO**

#### Article History

Received 17 October 2019 Accepted 10 May 2020

#### Keywords

Current-fed voltage doubler power factor correction rectifiers hybrid electric vehicle charging system

#### **ABSTRACT**

A current-fed bridgeless interleaved power factor correction rectifier with voltage-doubler characteristic is proposed for a hybrid electric vehicle charging system. The simulated efficiencies, Total current Harmonics current Distortion (THD $_{o}$ ), and Power Factor (PF) for the bridgeless interleaved Power Factor Correction (PFC) converter are presented in this paper. The differences of the simulated THD and PF between the proposed PFC boost converter and the conventional interleaved PFC boost converter are significant. The simulation results included a prototype boost converter converting universal AC input voltage 85–264 V to 400 V DC output at up to 3.4 kW load. The simulation results also demonstrate a power factor greater than 0.99 from a universal AC-line input 85–264 Vrms; THD <10% from a universal AC-line input 85–264 Vrms. The proposed converter achieved an average efficiency of 97% at 70 kHz switching frequency, 264 V input, and 0.5–3.4 kW output power. The proposed interleaved boost PFC rectifier exhibits an improved low-line efficiency compared with that of its conventional counterpart under 1.5 kW output power.

© 2020 The Authors. Published by Atlantis Press SARL.

This is an open access article distributed under the CC BY-NC 4.0 license (http://creativecommons.org/licenses/by-nc/4.0/).

#### 1. INTRODUCTION

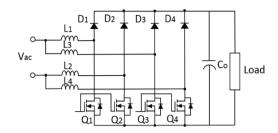

The low transfer efficiency occurs in low line condition for general conventional power factor correction rectifier. This drawback can be improved by proposing Power Factor Correction (PFC) with voltage doubler characteristic and the topology can be seen on Salmon [1] and Maksimovic and Erickson [2]. The Voltage doubler circuit applied in boost PFC converter to gain 400 V output was reported on Musavi et al. [3]. However, PFC circuit should have multiple switches to realize function of double voltage in low line condition, it is not suitable for server power due to the issues of efficiency, reliability, and cost. Besides, the electric vehicle with plug-in charging storage system can be charged through outside recycling system. The charging infrastructure always composes of AC/DC converter with power factor correction function in conjunction with series DC/DC buck converter structure. Preliminary stage AC/DC converter is important power stage module of electric vehicle (EV) battery charger as stated in Musavi et al. [3] is redrawn as Figure 1. The other literatures as Lai and Ho [4], Ryu et al. [5], Moon et al. [6] are the controlled the algorithm methodology related to EV application circuits and converters. The proposed PFC boost converter with voltage double characteristic improves efficiency of current interleave bridgeless PFC operated in low line and light load condition and meet input current harmonics specification as well. It can reach high power factor and high efficiency and suitable to apply for EV battery storage and charging system to have power reaching 3.4 kW.

### 2. OPERATING ANALYSIS

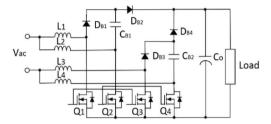

The proposed current fed bridgeless interleave PFC boost converter with voltage doubler characteristic is shown in Figure 2. The operating and steady-state circuit analysis of the novel PFC converter was implemented with the AC line input during the positive half cycle. In the symmetrical control operating period of positive half cycle, the test condition of duty cycle (0 < D < 0.5) is analyzed, and the test condition of duty cycle (0.5 < D < 1) will be neglected due to the similar behavior. We supposed that the semiconductor components are ideal and then the circuit operating of the proposed PFC in one switching cycle will be discussed.

A. The range of duty cycle (0 < D < 0.5)

In order to easy to obtain the stable analysis of the proposed PFC converter, the voltage and current operational waveforms are shown in Figure 3.

Period 1[ $t_0 - t_1$ ]: The ripple current of  $L_1$ ,  $L_3$

$$\Delta i_{L_1} = \frac{V_o - V_{AC}}{L_1 + L_3} \left( \frac{1}{2} - D \right) T_s \tag{1}$$

The ripple current of  $L_2$ ,  $L_4$

$$\Delta i_{L_2} = \frac{[(1-D)V_o - V_{AC}]}{L_2 + L_4} \left(\frac{1}{2} - D\right) T_s$$

(2)

Period 2[ $t_1 - t_2$ ]: The ripple current of  $Q_1$ ,  $Q_3$  and current of  $L_1$ ,  $L_3$  increase linearly.

Figure 1 | Bridgeless interleave PFC converter.

**Figure 2** The proposed current fed bridgeless interleave PFC boost converter with voltage doubler characteristic.

**Figure 3** Operational waveforms of proposed converter during duty cycle 0 < D < 0.5.

$$\Delta i_{L_1} = \frac{V_{AC}}{L_1 + L_3} DT_s \tag{3}$$

The ripple current of  $L_2$ ,  $L_4$

$$\Delta i_{L_2} = \frac{[V_{AC} - (1 - D)V_o]}{L_2 + L_4} DT_s \tag{4}$$

Combine (3) and (4), the total input ripple current  $\Delta I_{\rm in}$  is the ripple current of addition of  $L_1$ ,  $L_3$  and  $L_2$ ,  $L_4$

$$\Delta I_{\rm in} = \frac{[2V_{\rm AC} - (1 - D)V_o]}{L_1 + L_2} DT_s \tag{5}$$

Period 3[ $t_2 - t_3$ ]: The ripple current of  $L_1$ ,  $L_3$

$$\Delta i_{L_1} = \frac{V_o - V_{AC}}{L_1 + L_3} \left( \frac{1}{2} - D \right) T_s \tag{6}$$

The ripple current of  $L_2$ ,  $L_4$

$$\Delta i_{L_2} = \frac{[(1-D)V_o - V_{AC}]}{L_2 + L_4} \left(\frac{1}{2} - D\right) T_s \tag{7}$$

Period  $4[t_3 - t_4]$ :

The ripple current of  $Q_2$ ,  $Q_4$  and current of  $L_2$ ,  $L_4$  increase linearly as well.

$$\Delta i_{L_2} = \frac{V_{AC}}{L_2 + L_4} DT_s \tag{8}$$

When  $Q_1$ ,  $Q_3$  turn off, current of  $Q_1$  is zero and ripple current of  $Q_3$  is the same as that of  $L_3$  current of  $L_1$  turns to increase linearly

$$\Delta i_{L_1} = \frac{(V_{AC} - DV_o)}{L_1 + L_3} DT_s \tag{9}$$

Advance to combine (8) and (9), the total input ripple current  $\Delta I_{\text{in}}$  is the current of addition of  $L_2$ ,  $L_4$  and  $L_3$

$$\Delta I_{\rm in} = \frac{2V_{\rm AC} - DV_o}{L_1 + L_3} DT_s \tag{10}$$

B. The range of duty cycle (0.5 < D < 1)

In this state, the voltage and current operational waveforms are shown in Figure 4.

**Figure 4** Operational waveform of proposed converter during duty cycle 0.5 < D < 1.

Period 1[ $t_0 - t_1$ ]: The ripple current of  $Q_1$ ,  $Q_3$  and current of  $L_1$ ,  $L_3$  increase linearly.

$$\Delta i_{L_1} = \frac{V_{\text{AC}}}{L_1 + L_3} \left( D - \frac{1}{2} \right) T_s \tag{11}$$

The ripple current of  $Q_2$ ,  $Q_4$  and current of  $L_2$ ,  $L_4$  also increase linearly, as (12) stated

$$\Delta i_{L_2} = \frac{V_{AC}}{L_2 + L_4} \left( D - \frac{1}{2} \right) T_s \tag{12}$$

Period  $2[t_1 - t_2]$ : The ripple current of  $L_1$ ,  $L_3$  is

$$\Delta i_{L_1} = \frac{V_{AC}}{L_1 + L_3} (1 - D) T_s \tag{13}$$

At the meantime, the ripple current of  $L_3$ ,  $L_4$

$$\Delta i_{L_3} = \frac{\left(\frac{V_o}{2} - V_{AC}\right)}{L_2 + L_4} (1 - D) T_s \tag{14}$$

Combine (13) and (14), the total input ripple current  $\Delta I_{in}$  is the current of addition of  $L_1$ ,  $L_3$  and  $L_2$ ,  $L_4$

$$\Delta I_{\rm in} = \frac{\frac{V_o}{2}}{L_1 + L_3} (1 - D) T_s \tag{15}$$

Period  $3[t_2 - t_3]$ : current of  $L_1$ ,  $L_3$  increase linearly, as (16) stated

$$\Delta i_{L_1} = \frac{V_{AC}}{L_1 + L_3} \left( D - \frac{1}{2} \right) T_s \tag{16}$$

The ripple current of  $L_2$ ,  $L_4$  increase linearly as well.

$$\Delta i_{L_2} = \frac{V_{AC}}{L_2 + L_4} \left( D - \frac{1}{2} \right) T_s \tag{17}$$

Period  $4[t_3 - t_4]$ : The ripple current of  $L_1$ ,  $L_3$  is

$$\Delta i_{L_1} = \frac{\left(\frac{V_o}{2} - V_{3c}\right)}{L_1 + L_3} (1 - D) T_s \tag{18}$$

The ripple current of  $L_2$ ,  $L_4$

$$\Delta i_{L_2} = \frac{V_{AC}}{L_2 + L_4} (1 - D) T_s \tag{19}$$

Combine (18) and (19), the total input ripple current  $\Delta I_{in}$  is the ripple current of addition of  $L_2$ ,  $L_4$  and  $L_1$ ,  $L_3$

$$\Delta I_{\rm in} = \frac{\frac{V_o}{2}}{L_1 + L_3} (1 - D) T_s \tag{20}$$

# 3. SYSTEM VOLTAGE CONVERSION ANALYSIS

According to the circuit analysis of the proposed PFC converter, the equivalent equation will reveals when the current of  $L_2$ ,  $L_4$  increase

$$V_{\rm AC} = L_2 \frac{di_{\rm L_2}}{dt} + L_4 \frac{di_{\rm L_4}}{dt} \tag{21}$$

Based on Equation (21), we suppose  $L = L_2 = L_4$  and

$$\frac{di_{L_2}}{dt} = \frac{V_{AC}}{2L} \tag{22}$$

When current of  $L_2$ ,  $L_4$  decrease, the equivalent equation refer to (23) as

$$V_{\rm AC} = \frac{V_o}{2} - L_2 \frac{di_{L_2}}{dt} - L_4 \frac{di_{L_4}}{dt}$$

(23)

From Equation (23), we suppose  $L = L_2 = L_4$  and

$$\frac{di_{L_2}}{dt} = \frac{1}{2L_2} \left( \frac{V_o}{2} - V_{AC} \right)$$

(24)

To analyze the current of  $L_{\scriptscriptstyle 2}$  via the volt-second balance principle in Figure 4.

$$V_{AC}DT_s + \left(V_{AC} - \frac{V_o}{2}\right)(1 - D)T_s = 0$$

(25)

The voltage conversion ratio is obtained

$$\frac{V_o}{V_{AC}} = \frac{2}{1 - D} \tag{26}$$

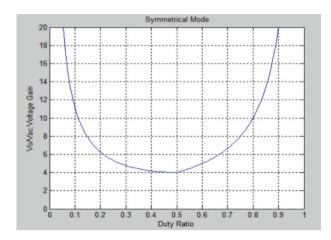

According to the above voltage conversion equation, higher voltage gain ratio can be obtained while duty ratio D > 0.5 and the current of  $L_2$  decrease relatively according to Equation (24). Moreover, we can actually implement the similar derivation for the range of duty cycle (0 < D < 0.5). Eventually, the voltage conversion ratio is obtained in below

$$\frac{V_o}{V_{AC}} = \frac{1}{D - D^2} \tag{27}$$

According to Equation (27), we can probably set up the lowest limit of duty ratio for avoiding the uncontrolled duty ratio in the proposed converter. Setting the duty ratio to 10%, and then the output voltage  $V_o$  is 11 times of  $V_{\rm AC}$ . As a result, the minimum duty ratio of the proposed converter will be 10% and the voltage gain is raised to 11. Figure 5 illustrates the voltage conversion gain ratio of the proposed converter.

#### 4. SIMULATION RESULT

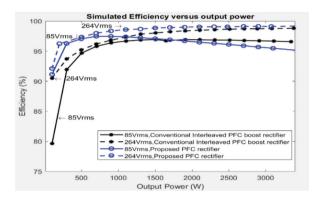

A set of 3.4 kW prototype was designed including design includes full range input 85–264 Vrms and 400 V/8.5 Å output electrical

Figure 5 | Voltage conversion gain ratio of the proposed converter.

**Figure 6** | Simulation result of comparison of efficiency of the proposed converter and conventional interleave bridgeless PFC converter.

characteristic. Figure 6 was the efficiency comparison for AC input of 85 and 264 Vrms respectively. In this Figure, when the power lower than 1.5 kW at 85 Vrms input condition, the efficiency of the proposed converter higher than the conventional one. The reason is that the proposed converter operates in double voltage mode (voltage conversion ratio  $V_o/V_{\rm AC}=2/(1-D)$ ) at duty ratio D>0.5. The switches conduction loss of the proposed converter is about two-third of the conventional one. The switching loss of the switches and reverse recovery loss of the diodes are lower as well. This is because the voltage of switches and diodes are half of the output voltage. Furthermore, the efficiency of the proposed converter is higher than the conventional one when the converters operate in high line condition (264 Vrms).

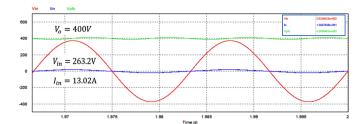

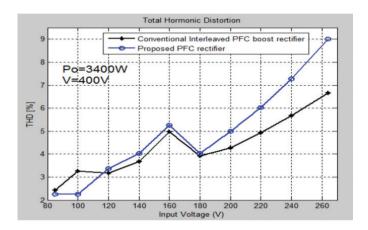

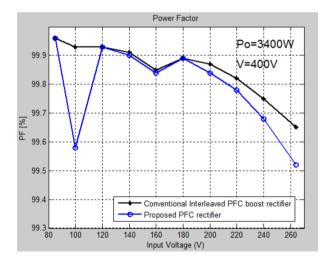

In this condition, the duty ratio is always higher than 0.5 and the voltage doubler characteristic is revealed. The simulation waveforms of output voltage  $V_o$  at  $P_o=3.4~\rm kW$  and  $V_o=400~\rm V$ ; input voltage  $V_{\rm in}$  and input current  $I_{\rm in}$  was stated in Figure 7. Based on the result that the efficiency of the proposed converter can reach 98% during 264 Vrms input voltage and out power of 0.5–3.4 kW condition, heat sinks and active cooling system can be reduced. Charging time and cost of power conversion can be reduced as well. Figures 8 and 9 simulate THD, and PF during input voltage range 85–264 Vrms. In Figure 8, it can be observed that the low line operated THD of proposed converter is lower than the conventional one while it is opposite when operated in high line. The PF of the proposed converter revealed in Figure 9 is lower than the conventional one.

**Figure 7** | The simulation waveforms of output voltage  $V_o$  at  $P_o=3.4$  kW and  $V_o=400$  V; input voltage  $V_{\rm in}$  and input current  $I_{\rm in}$  for the proposed converter.

**Figure 8** The comparison of THD simulation result of  $P_o = 3.4$  kW and  $V_o = 400$  V for both converters.

**Figure 9** The comparison of PF simulation result of  $P_o = 3.4$  kW and  $V_o = 400$  V for both converters.

#### 5. CONCLUSION

In this paper, a current fed PFC boost converter with voltage doubler characteristic was proposed to apply for preliminary stage AC to DC converter of hybrid electric vehicle. The proposed PFC converter possesses high conversion efficiency when operates in low line condition. The proposed converter prototype was simulated and analyzed including efficiency, THD, and PF. Comparison was made for full-range input voltage, full load 3.4 kW and 400

V output test conditions. The efficiency reaches 97% when it was operated at 70 kHz switching frequency, 264 V input voltage, and  $0.5-3.4\,\mathrm{kW}$  output power. The proposed converter possesses higher efficiency than conventional converter and suitable for applying as option of electric vehicle industry.

## **CONFLICTS OF INTEREST**

The authors declare they have no conflicts of interest.

#### **REFERENCES**

- [1] J.C. Salmon, Circuit topologies for single-phase voltage-doubler boost rectifiers, IEEE Trans. Power Electron. 8 (1993), 521–529.

- [2] D. Maksimovic, R. Erickson, Universal-input, high-power-factor, boost doubler rectifiers, Proceedings of 1995 IEEE Applied

- Power Electronics Conference and Exposition (APEC), IEEE, Dallas, TX, USA, 1995, pp. 459–465.

- [3] F. Musavi, W. Eberle, W.G. Dunford, A high-performance single-phase bridgeless interleaved PFC converter for plug-in hybrid electric vehicle battery chargers, IEEE Trans. Ind. Appl. 47 (2011), 1833–1843.

- [4] Y.S. Lai, K.M. Ho, FPGA-based digital-controlled power converter with universal input meeting 80 plus platinum efficiency code and standby power code for server power applications, 2012 International Conference on Renewable Energy Research and Applications (ICRERA), IEEE, Nagasaki, Japan, 2012, pp. 1–6.

- [5] S.H. Ryu, D.H. Kim, M.J. Kim, J.S. Kim, B.K. Lee, Adjustable frequency-duty-cycle hybrid control strategy for full-bridge series resonant converters in electric vehicle chargers, IEEE Trans. Ind. Electr. 61 (2014), 5354–5362.

- [6] D. Moon, J. Park, S. Choi, New interleaved current-fed resonant converter with significantly reduced high current side output filter for EV and HEV applications, IEEE Trans. Power Electr. 30 (2015), 4264–4271.

#### **AUTHORS INTRODUCTION**

#### Prof. Chih-Chiang Hua

He (S'91–M'92) received the BS degree in Electrical Engineering from National Cheng Kung University, Tainan, Taiwan, in 1984, and the MS and PhD degrees in Electrical Engineering from the University of Missouri, Columbia, MO, USA, in 1990 and 1992, respectively. Since 1992, he has been with the National Yunlin University of Science and Technology, Douliou,

Taiwan, where he is currently a Professor at the Department of Electrical Engineering. His research interests include power electronics converters, uninterruptible power supplies, and photovoltaic/wind energy systems. He is a Member of the IEEE Power Electronics and the IEEE Industrial Electronics Societies.

#### Prof. Ching-Chun Chuang

He received the PhD degree in Electronics Engineering from National Taiwan University of Science and Technology, Taiwan, in 2013. Since 2017, he has been an Associate Professor at Faculty of College of Future, Yunlin University of Science and Technology, Taiwan. His

research interests include power electronics, digital control and robot applications.

#### Dr. Hung-Chi Lee

He received the MS and PhD degrees in Electronics Engineering from National Taiwan University of Science and Technology, Taiwan, in 2007 and 2013, respectively. He is currently a Postdoctoral Researcher of National Taiwan University of Science and Technology, Taiwan. His research interests include power electronics and EMC.

# Prof. Chih-Wei Chuang

He (1979) received the PhD degree in Electrical Engineering from National Yunlin University of Science and Technology, Taiwan, in 2017. Since 2017, he has been an Associate Professor at Faculty of College of Future, Yunlin University of Science and Technology, Taiwan. His research interests include the design and implementation of

renewable energy sources and active power filters.

#### Mr. Chuan-Ming Niu

He received Bachelor's degree in Engineering (Energy Information Group) from Southern Taiwan University of Science and Technology in Taiwan in 2019. He currently study in a Master's degree from the Graduate School of Engineering, National Yunlin University of Science and Technology, Taiwan. His research interests

include Power Electronics and Power Systems.